# Oscillator Impact on PDV and Design of Packet Equipment Clocks

ITSF 2010

Peter Meyer

peter.meyer@zarlink.com

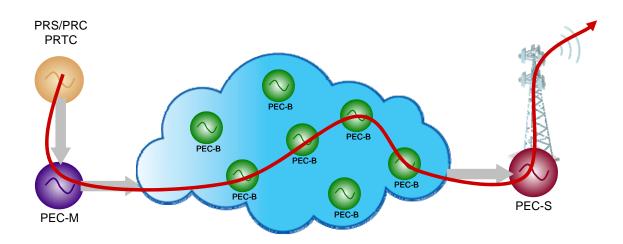

## Protocol Layer Synchronization

- When deployed and inter-connected within the packet network the packet equipment clocks will allow frequency, phase and time to be transferred over the packet network

- Different types of packet equipment clocks (PEC)

- PEC-M the input is physical timing and the output is packet timing signal

- PEC-B the input is a packet timing signal and the output is a packet timing signal

- PEC-S the input is a packet timing signal and the output is a physical timing signal

### Frequency & Time Transfer over PSN

#### Two approaches

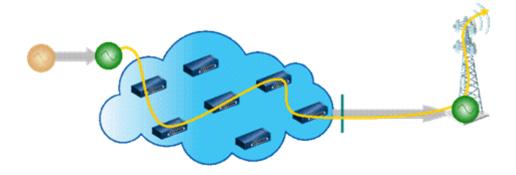

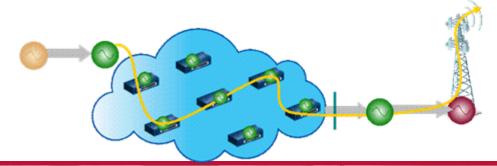

A PSN may be inserted between the server and client, that is not aware of protocol layer synchronization packets (e.g. IEEE 1588-2008)

The PSN has 'on-path support' where each switch / router is aware of protocol layer synchronization packets (e.g. IEEE 1588-2008)

## PEC Model & Generic Requirements

## Protocol Layer EC Functional Model

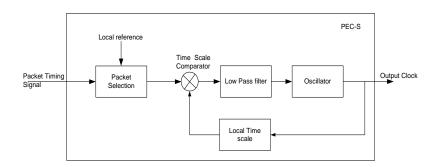

- ITU-T G.8263 (draft) Annex includes a functional model of a PEC-S packet-based clock

- PEC differs from traditional EC with introduction of a packet selection block has been included

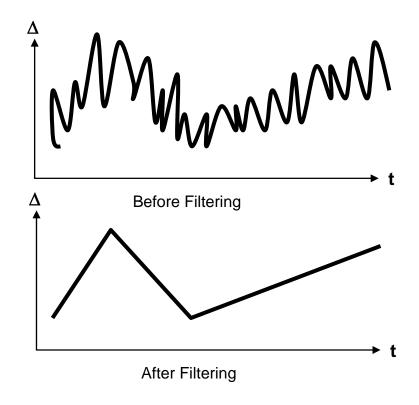

- The PLL filters the network wander with a low pass filter

- This means the PLL acts as a high pass filter for the local XO

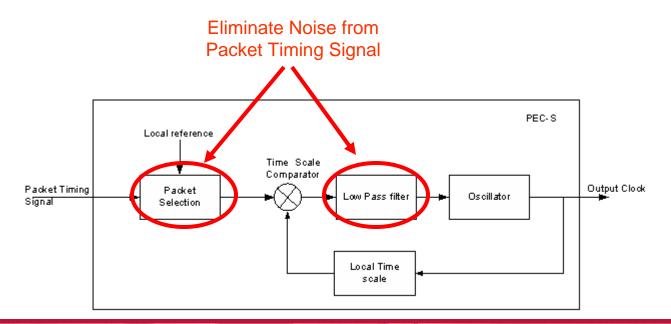

## PEC-S Functional Model: Packet Selection & Low Pass Filter

- Goal of the packet selection block is to select from all the input packets to the packet equipment clock a certain subset that are the least affected by the packet switched network

- These packets would thus best reflect the timing signal at the transmitter

- Both the packet selection block and the low pass filter function to remove noise from the packet timing signal to faithfully re-create the timing source

- The 'cleaned' timing signal can then be used to discipline the local oscillator

## Equipment Clock Specifications

- Definition of EC

- Jitter & Wander Generation

- Jitter & Wander Transfer

- Jitter & Wander Tolerance

- Holdover

- Transients

- Freerun

- Oscillator dominant factor in meeting parts of the specification

- Wander Generation (both MTIE & TDEV)

- Holdover Stability (both constant & variable temperature)

- Freerun Accuracy

### Oscillator-Dependent EC Characteristics

#### Wander Generation

- The amount of wander generated by the EC when locked to an ideal reference

- Oscillator noise measured in the time domain using MTIE & TDEV metrics

#### Holdover Stability

- The stability of an EC when after losing lock to its input reference

- Oscillator drift due to ageing, temperature, voltage and other effects measured in the frequency domain

### Freerun Accuracy

- The accuracy of an EC without using an input reference

- Oscillator error due to all error sources in the frequency domain

## Example: Oscillator Requirements for Stratum 3E

- Looking at Stratum 3E EC, with a focus on the oscillator, yields the following requirements to be met by the oscillator specification

- Other ECs (Stratum 3, SMC, etc.) would have similar requirements

- Requirements

- Free-run Frequency Accuracy

- ±4.6 ppm

#### **Wander Generation**

- MTIE & TDEV masks specified in ITU-T G.812 Type III & Telcordia GR-1244-CORE Stratum 3E, using 1 mHz clock bandwidth

- Holdover Stability

- ± 1 ppb/day at constant temperature (1.16x10^-5 ns/s^2)

- 10 ppb over temperature range

## Design Considerations of Packet Equipment Clock

## PEC Design Considerations

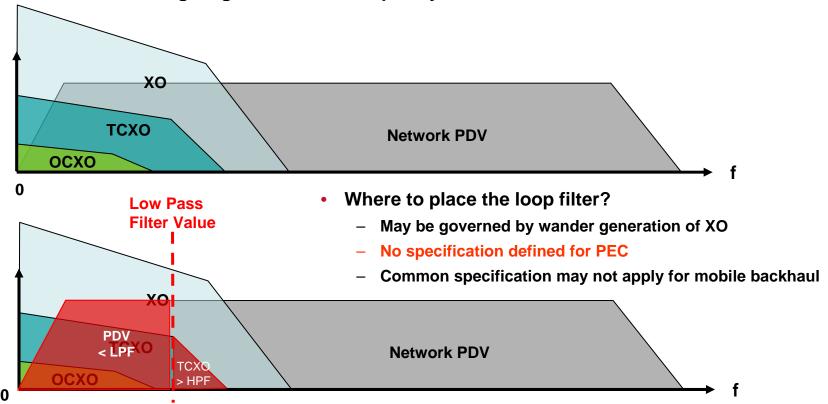

- Trade-off between PDV noise (LPF) and XO noise (HPF)

- Effects of XO on packet selection

- Possible PEC characteristics & XO requirements

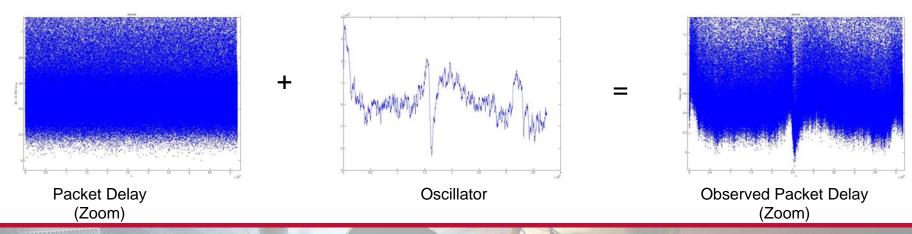

### Trade-off Between PDV and XO

- PDV and XO noise can be shown on a frequency spectrum plot

- Network PDV has wide frequency spectrum

- Ramp test case has 12 uHz fundamental frequency

- On/Off test case has 139 uHz fundamental frequency

- XO has increasing magnitude at low frequency

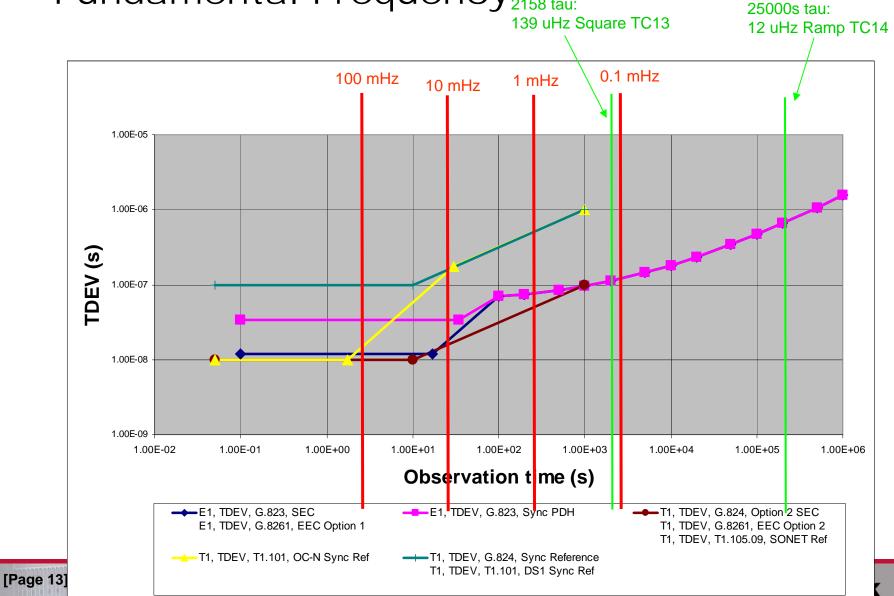

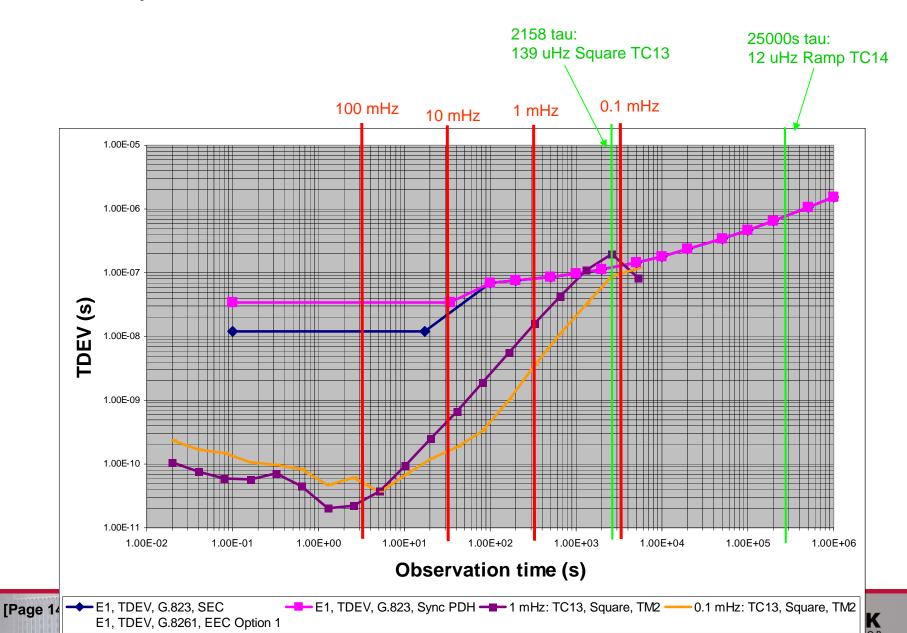

Ramp (TC13) and Square (TC14) Fundamental Frequency<sub>2158 tau:</sub>

SEMICONDUCTOR

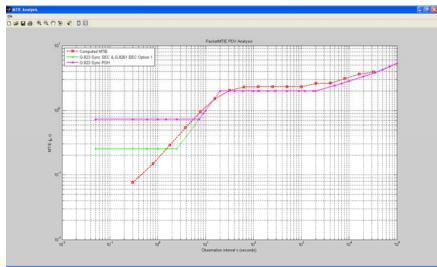

## Ramp (TC13) TDEV

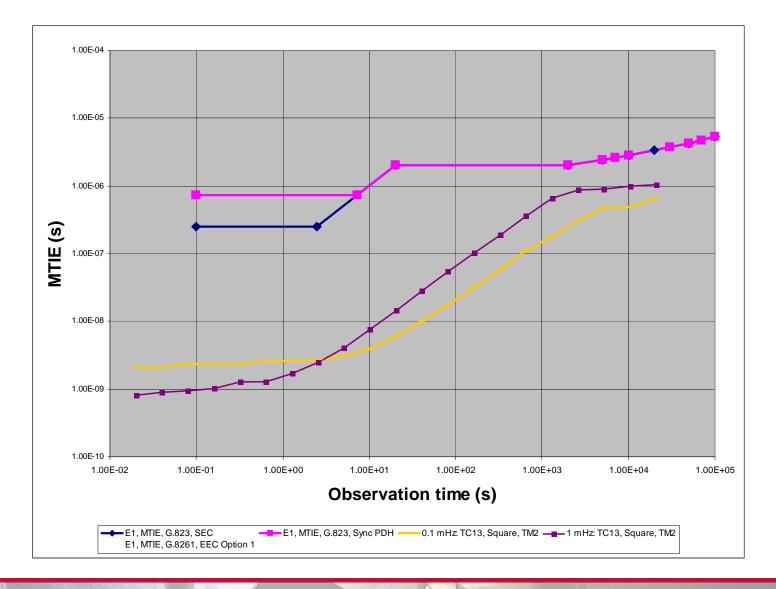

## Ramp (TC13) MTIE

## Relationship between PDV, XO and Clock Bandwidth

### Wander Generation vs. Clock Bandwidth

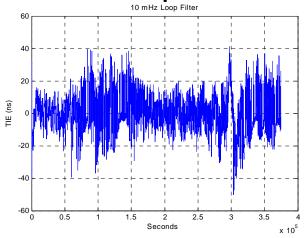

With a 10 mHz loop filter this oscillator has a low TIE and TDEV noise

[Page 17]

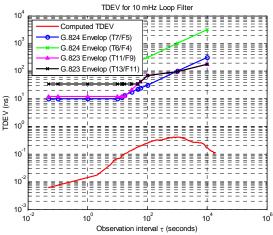

- With a 1 mHz loop filter there is significantly MORE noise contributed by the oscillator → A lower the loop filter will filter LESS oscillator noise

- Cannot keep lowering the loop filter to be more robust against PDV without increasing the cost of the equipment!

### Wander Generation vs. Clock Bandwidth

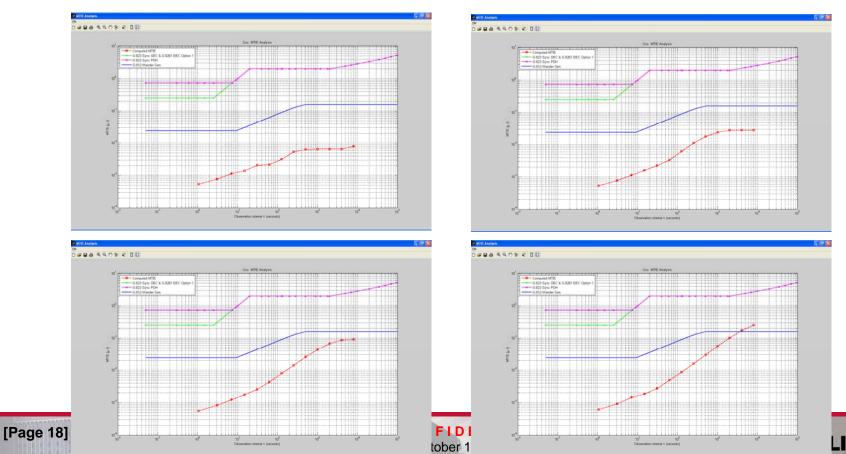

#### Wander Generation MTIE

- 3 mHz, 1 mHz, 0.3 mHz & 0.1 mHz clock bandwidths

- 1 mHz  $\rightarrow$  0.1 mHz results in 10x more wander @ 8000 s

### Wander Generation vs. Clock Bandwidth

#### Wander Generation TDEV

- 3 mHz, 1 mHz, 0.3 mHz & 0.1 mHz clock bandwidths

- 1 mHz  $\rightarrow$  0.1 mHz results in >4x more wander @ 1000 s

## Oscillator Selection Impact on Packet Selection

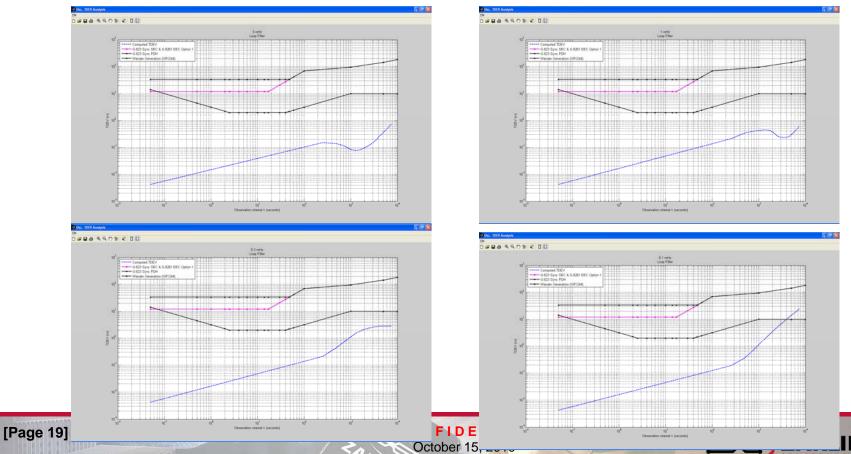

### Packet Selection vs. Oscillator

- 'Cleaned' packet timing signal used to discipline local oscillator

- Will the oscillator movement impact on the packet selection to reduce estimated performance

- If there was originally a stable floor delay, how does it appear to move based on a non-ideal local oscillator?

- What is inter-packet gap between selected packets and how should this be adjusted to match the non-ideal local oscillator?

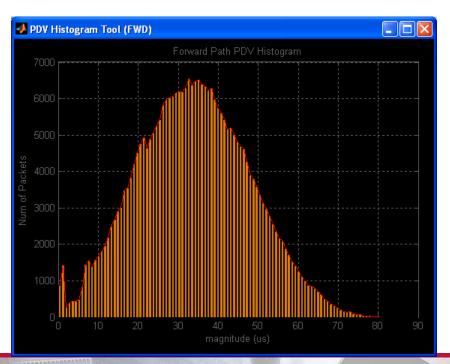

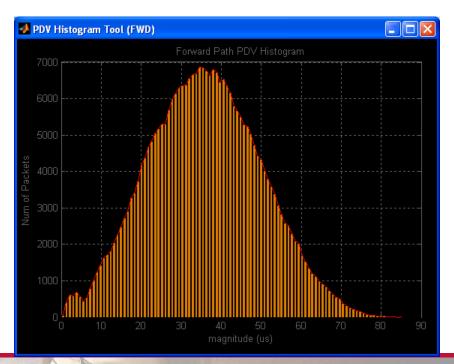

# Packet Selection vs. Oscillator: Histogram

- Two Oscillators

- Same Clock Bandwidth, Packet Selection, PDV

Observation: FWPR is reduced

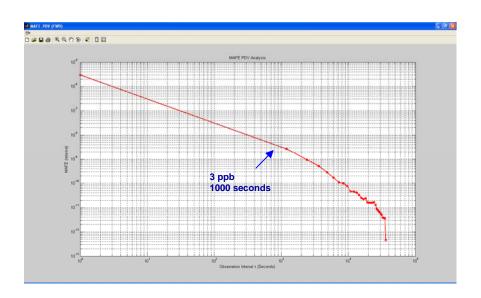

## Packet Selection vs. Oscillator: MAFE

- Two Oscillators

- Same Clock Bandwidth, Packet Selection, PDV

- Observation: Frequency accuracy not greatly impacted for typical mobile backhaul application

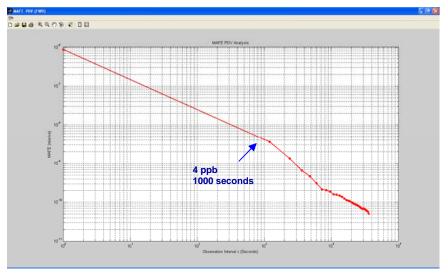

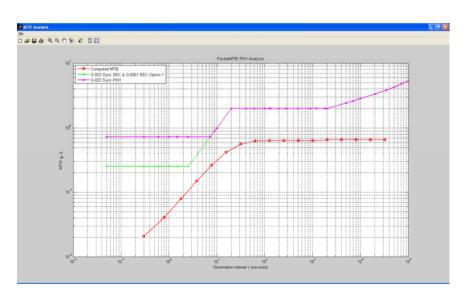

# Packet Selection vs. Oscillator: Packet Timing Signal MTIE

- Two Oscillators

- Same Clock Bandwidth, Packet Selection, PDV

- Observation: MTIE substantially impacted relative to synchronization performance requirements

## Packet Selection vs. Oscillator & Clock Bandwidth

#### Summary

- XO directly impacts wander generation conformance, a parameter defined in the time domain

- Absence of time domain characterization in XO makes component selection difficult

- Time domain is significantly impacted by oscillator selection vs. packet selection & clock bandwidth

- Lack of standard for PEC results in freedom to optimize clock bandwidth based on custom design choices

- Frequency domain performance is less impacted by oscillator selection vs. packet selection & clock bandwidth

- Specifically the mobile backhaul application (< 50 ppb accuracy)</li>

- Target application is very forgiving of XO selection

- Lowest hanging fruit

- PEC for applications requiring only frequency accuracy, such as mobile basestation, are easier to design based on traditional XO characterization information

## Thank-you for Your Time & Attention

**ITSF 2010**