### >BUSINESS MADE **SIMPLE**

Investigation and testing of Layer 2 Timing Distribution using Ethernet Provider Backbone Transport (PBT)

Simon Brueckheimer – Consultant Architect – CTO Office Michel Ouellette – System Architect – CTO Office ITSF

Prague, November 14-16, 2006

- > Investigation's goals

- > Wireless backhaul reference and performance requirements

- > Provider Backbone Transport (PBT) attributes

- > Test results (IEEE1588, ACR) in a PBT reference network

- Immunity to low priority background step loads

- Immunity to high priority CES load

- PBT failover and restoration

- Fibre ring failover and restoration

- > How PBT addresses concerns about Layer 2 Timing Distribution

- > Further engineering considerations

- > Conclusions

- > To test the state-of-the-art in packet based layer 2 timing distribution over carrier grade Ethernet network

- Engineered with Provider Backbone Transport (PBT)

- > To establish acceptable performance to meet the demands of wireless backhaul

- > To verify solution's completeness

- Synchronisation performance alongside challenging impairments

- Meet or exceed availability targets of PDH and SDH networks

- Ease of implementation: simple network engineering and operation

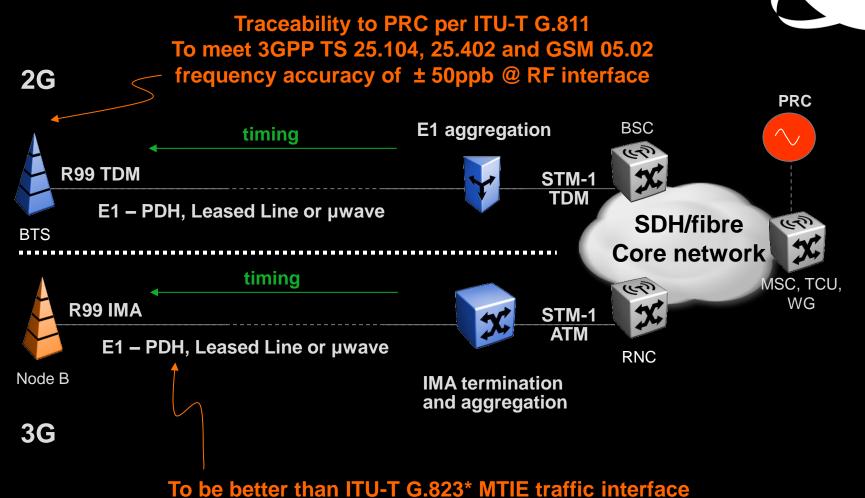

### **Current Wireless Backhaul Deployment**

\*Similar requirements exist for T1 interfaces

#### **Future Wireless Backhaul Deployment**

To meet all current requirements (previous slide) and requirements being established in ITU-T G.8261 **2G PRC** Timing @ layer 2 (IEEE1588, ACR) **BSC R99 TDM TDM PWE** STM-1 TDM CO aggregation Eth/fibre BTS **PBT Ethernet** Core network Network MSC, TCU, (4) WG **R99 IMA** STM-1 **ATM ATM PWE** O aggregation **RNC** Cell Site and TD Node B NTE Timing @ layer 2 (IEEE1588, ACR) **3G**

Ethernet metro and core can be built using PBT to carry all service (not just wireless backhaul) over one network

Ethernet network can optionally provide Layer 1 synchronisation

#### **Provider Backbone Transport (PBT)**

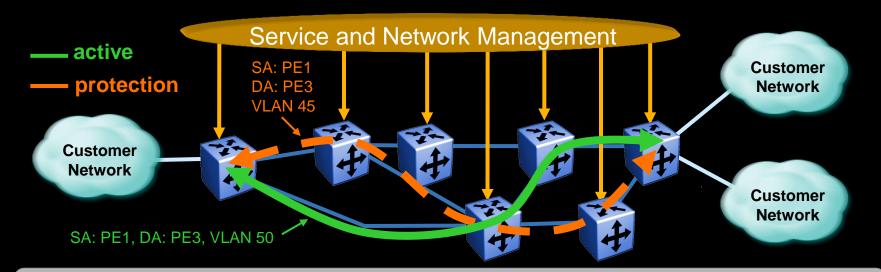

- > PBT engineers protected point-to-point Ethernet connections

- Management and Network Admission Control sets up active and protected connections

- Both paths (active, protection) are monitored by control frames: 35 to 50ms switchover

- > PBT ensures tight resource control of the Ethernet network

- Forwarding, Scheduling, Policing in switch assures Network Admission Control (NAC)

- > PBT secures the network by frame encapsulation at edge

- Carrier addresses isolated from customer prevents eavesdropping and DoS

PBT provides a deterministic environment for multiple services on the same network, and is a standard in ITU, IETF, IEEE, DSL Forum and TMF

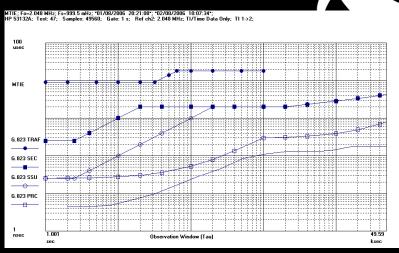

### **DUT (Back-to-back) Baseline Performance**

#### IEEE1588: FFoFF\* ± 3 to 4ppb; MTIE 100ns/1000s (180ns ref. T1)

Providing time and frequency synchronisation

ACR/CES: FFoFF\* ± 12 to 16ppb; MTIE 900ns/1000s (1.6µs ref. T1)

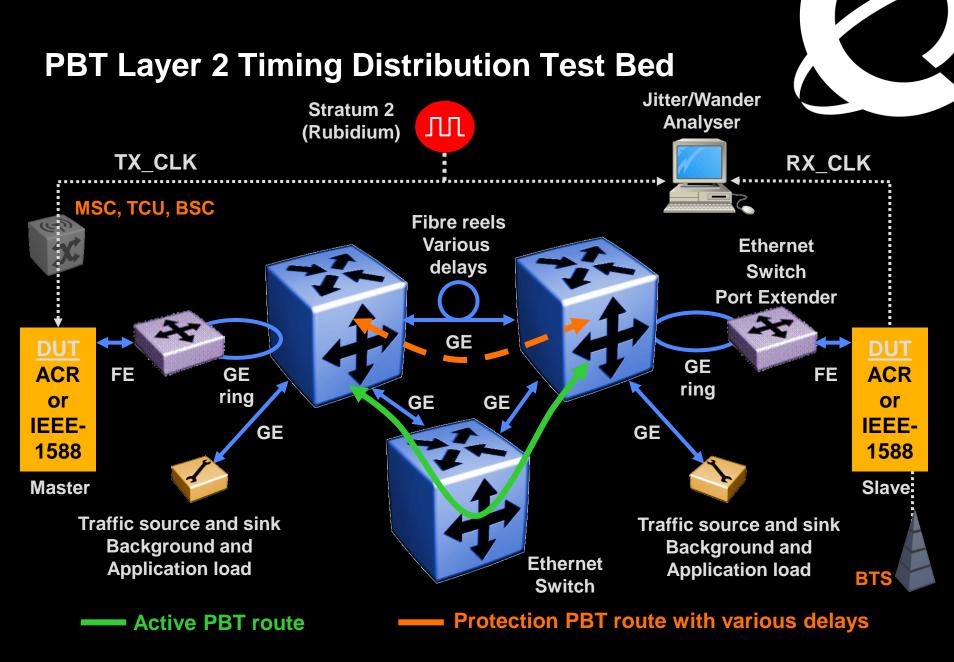

## Disciplined IEEE and ACR/CES PBT with low priority traffic overloads

- > IEEE1588 and ACR/CES traffic marked priority 6 (strict-sense)

- > Background load traffic priority 0 (best effort preemptable)

- > Load applied/removed

- 5 to 10 minute intervals

- 100% and 200% overload GE port rate

- Load fixed packet size = 64 octets (IEEE1588 = 64 octets)

- Quiescent delay = 51µs, PDV spread = 3µs, PLR = 0%

- 200% loaded delay = 115μs, PDV spread = 20μs, PLR = 0%

- Load fixed packet size = 1500 octets (ACR/CES = 318 octets)

- Quiescent delay = 42μs, PDV spread = 3μs, PLR = 0%

- 100% loaded delay =  $97\mu s$ , PDV spread =  $10\mu s$ , PLR = 0%

- 200% loaded delay = 105μs, PDV spread = 20μs, PLR = 0%

Investigates how well the PDV is attenuated by the application

## Disciplined IEEE and ACR/CES PBT with low priority traffic overloads

FFoFF

≈ back-to-back

± 3ppb ≈ back-to-back

#### <u>ACR</u>

MTIE

1µs/1000s (2.2µs ref. T1)

≈ back-to-back

FFoFF

± 12ppb ≈ back-to-back

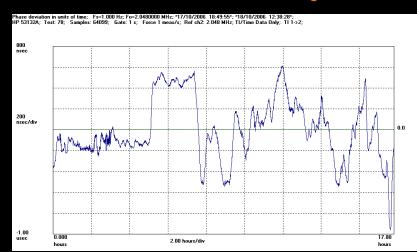

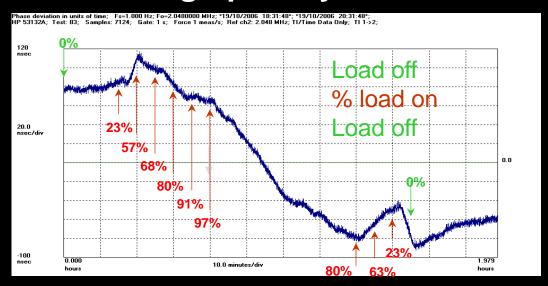

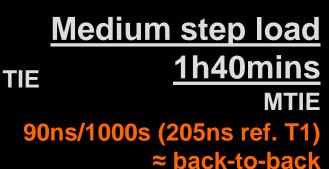

## Disciplined IEEE1588 PBT with high priority CES traffic load

- > IEEE1588 traffic marked priority 6 (strict-sense)

- > CES load traffic marked priority 6 (strict-sense)

- CES traffic is bidirectional

- > Load applied, and stepped up/down

- 5 minute intervals

- 5 57% steps, between 0% and 97% of GE port rate

- 97% load held for 40 minutes, and also 9 hours

- Load fixed packet size = 318 octets (SAToP)

- > IEEE1588 traffic impairment

- Quiescent delay = 51μs, PDV spread = 3μs, PLR = 0%

- 97% loaded delay = 62μs, PDV spread = 5μs, PLR = 0%

Investigates how well IEEE1588 timing distribution will operate with large amounts of CES traffic, in medium/large switched steps

## Disciplined IEEE1588 PBT with high priority CES traffic load

FFoFF ± 11ppb > back-to-back

### Large step load Held 9 hours

MTIE

600ns/1000s (1µs ref. T1)

> back-to-back

Still under G.8261 mask

**FFoFF**

± 11ppb > back-to-back

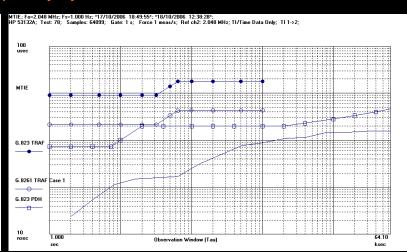

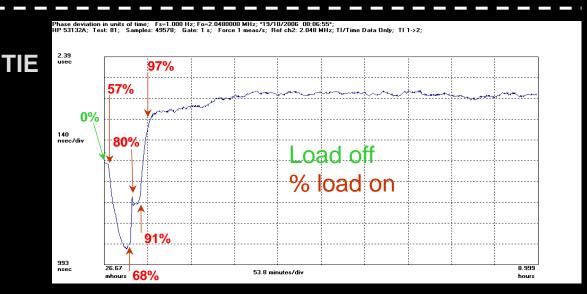

# Disciplined ACR/CES PBT with high priority CES traffic (over)load

- > ACR/CES traffic marked priority 6 (strict-sense)

- CES traffic is bidirectional

- > Load applied, and stepped up/down

- 2 5 minute intervals

- 10 50% steps, between 0% and 97% of GE port rate

- Load fixed packet size = 318 octets (SAToP)

- > ACR/CES traffic impairment

- Quiescent delay = 42μs, PDV spread = 3μs, PLR = 0%

- 97% loaded delay = 51µs, PDV spread = 5µs, PLR = 0%

- > Deliberate overload of 102%, PLR = 7%

- Reversion to 97%, demonstrating re-acquisition under load conditions

Investigates how well ACR/CES timing recovery will operate normally Overload demonstrates why Network Admission Control is essential

### **Disciplined ACR/CES**PBT with high priority CES, and a deliberate overload

System goes into holdover on overload, i.e. when Packet Loss Ratio rises above nominal

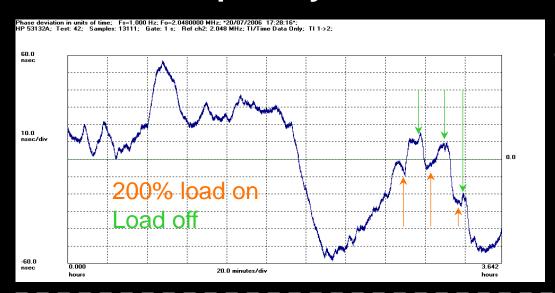

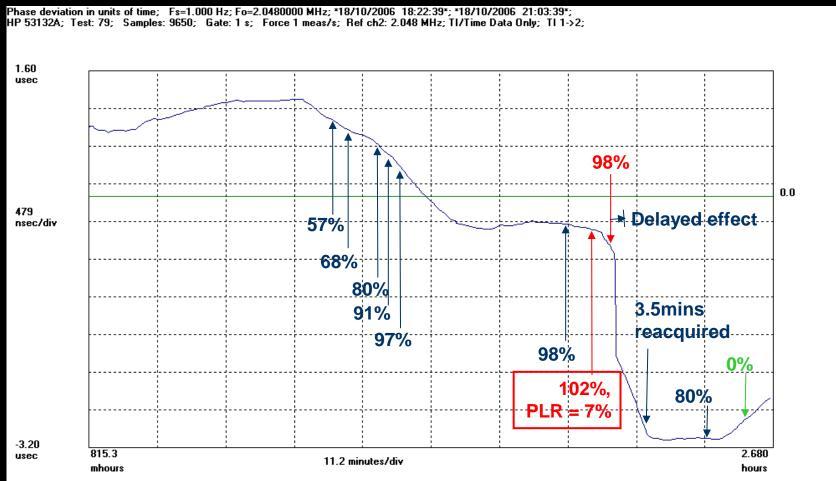

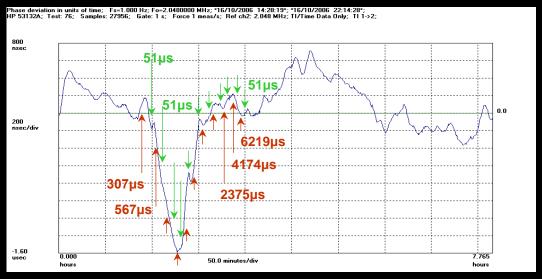

## Disciplined ACR/CES PBT failover with various path delay changes

- > Failover to a back-up route within 35-50ms

- > Delay on back-up route set between 300µs and 6600µs (1300km), steps of 260µs

- > Successive failover and restoration at 10 minute intervals, 5 minutes in failover

- > After restoration at each interval the back-up route delay was incremented

Investigates how well ACR/CES timing recovery will operate when failover occurs and the path delay changes

# Disciplined ACR/CES PBT failover with various path delay changes

TIE

Failover – to delay path (300µs to 6600µs, steps of 260µs or greater) Restoration to direct path (51µs)

MTIE

± 18ppb ≈ back-to-back

**FFoFF**

1.5µs/1000s (2.2µs ref. T1) ≈ back-to-back

Failover and restoration has been successfully achieved carrying live GSM calls, with no call drop or loss of synchronisation

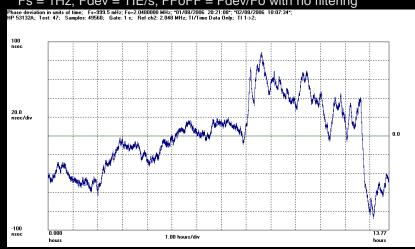

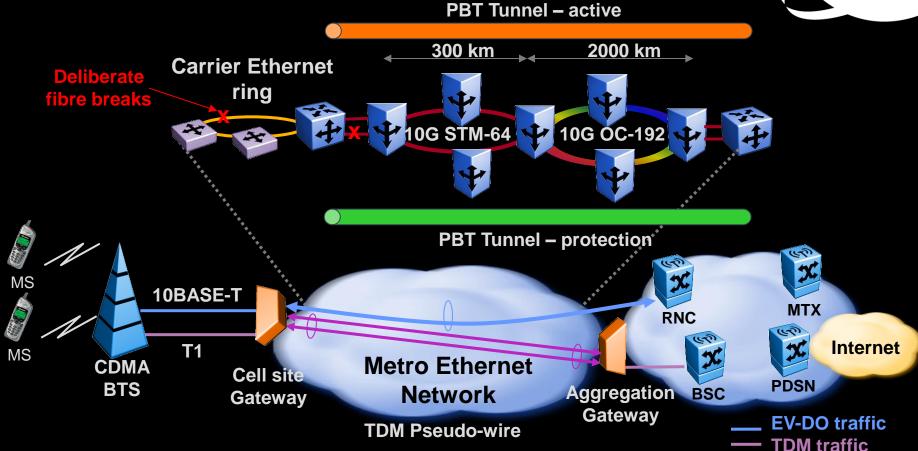

### **CDMA BTS Backhaul Live PBT Network**

No slips reported for over 1 week duration in CDMA BTS backhaul T1 jitter & wander within interface specification network limits

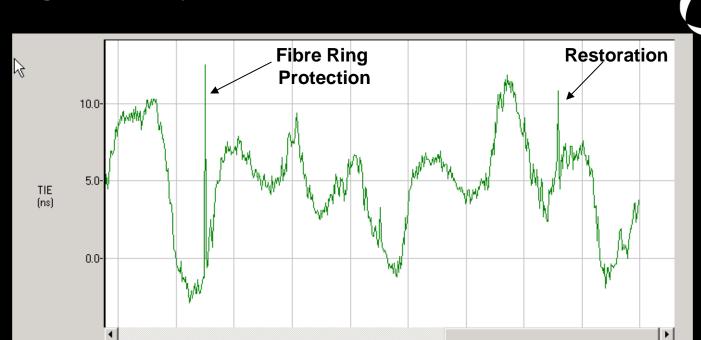

### **CDMA BTS Backhaul** Fibre Ring Resiliency

- Agilent

40.0

47.5

50.0

Elapsed time (s)

45.0

Protection & restoration switch on Carrier Ethernet ring did not impact wander generation at the cell-site gateway

52.5

4.2 ns

55.0

60.0

57.5

# Layer 2 Timing Distribution PBT is necessary to address impairments

- > Load and PDV

- PBT guards all service routes against overload

- Can maintain service route utilisation at any desired operating maximum via NAC

- Layer 2 timing distribution is marked Highest Priority, minimising PDV to just μs

- > Low-frequency wander

- Only CES or other <u>uniform bidirectional traffic</u> shares same route at same priority

- Other traffic of bursty or varying profile (mobile data) restricted to lower priorities

- > Stabilisation period

- No overload or service interruption means no loss of synchronisation in service

- > Changes in end-to-end delay

- PBT guarantees symmetrical delay (normal/failover) both ways are co-routed

- Back-up path meets same criteria for load and PDV as primary path

- Contributes considerably towards Layer 2 timing distribution

- > Security

- PBB address encapsulation at edge of PBT guarantees no eavesdropping or DoS

- > Each switch model has idiosyncrasies, e.g.

- Higher PDV than theory predicts

- Software based scheduling may introduce delay artefacts

- PDV may be a skewed distribution: mean close to maximum delay

- Load direct A B can also affect PDV in direction B A

- Most switches have a common fabric for both directions

- > Different vendor's switches yield different results

- > Standards must go further than specifying load tests alone

- Network Impairment Emulators are now available that can establish the operating limits of Layer 2 timing

- > Tests specified in absolute terms of path delay changes and PDV limits (min, max, mean and sigma)

- Repeatable

- Transferable targets between labs

- Layer 2 timing vendors, switch vendors, and network engineers

- > PBT provides an ideal environment to ensure the performance of Layer 2 Timing Distribution technologies

- Management layer Network Admission Control prevents overload

- Uniform traffic (ACR/CES, IEEE1588+CES) can be as high as 97% load

- Non-uniform traffic sent at lower priorities minimises interference

- Failover switching times as fast as SONET, SDH, and WDM fibre

- · Security via flexible VPN model with edge carrier address isolation

- > Tests conducted so far with ACR and IEEE1588 over PBT show that both can achieve wireless backhaul synchronisation requirements

- > Further soak tests are planned in the coming months, including failover tests with IEEE1588

Live calls and data download have been successfully made over PBT on GSM and CDMA networks, using Layer 2 Timing Distribution and CES All equipment worked in specification